Product Summary

The XC4044XLA-09HQ304I high-performance, high-capacity Field Programmable Gate Array (FPGA) provides the benefits of custom CMOS VLSI, while avoiding the initial cost, long development cycle, and inherent risk of a conventional masked gate array. It has reduced power requirements compared to equivalent XL devices. The smaller die of the device directly reduces clock delays and the delay of high-fanout signals. The reduction in clock delay llows improved pin-to-pin I/O specifications.

Parametrics

Electrical characteristics: (1)XLA Devices Require 3.0 - 3.6 V (VCC); (2)XV Devices Require 2.3- 2.7 V (VCCINT)and 3.0 - 3.6 V(VCCIO); (3)5.0 V TTL compatible I/O; (4)3.3 V LVTTL, LVCMOS compliant I/O; (5)5.0 V and 3.0 V PCI Compliant I/O; (6)12 mA or 24 mA Current Sink Capability; (7)Safe under All Power-up Sequences; (8)XLA Consumes 40% Less Power than XL; (9)XV Consumes 65% Less Power than XL; (10)Optional Input Clamping to VCC (XLA) or VCCIO (XV).

Features

Features: (1)System-featured Field-Programmable Gate Arrays: Select-RAMTM memory: on-chip ultra-fast RAM with Synchronous write option and Dual-port RAM option; Flexible function generators and abundant flip-flops; Dedicated high-speed carry logic; Internal 3-state bus capability; Eight global low-skew clock or signal distribution networks; (2)Flexible Array Architecture; (3)Low-power Segmented Routing Architecture; (4)Systems-oriented Features: IEEE 1149.1-compatible boundary scan; Individually programmable output slew rate; programmable input pull-up or pull-down resistors; Unlimited reprogrammability; (5)Read Back Capability: Program verification and internal node observability.

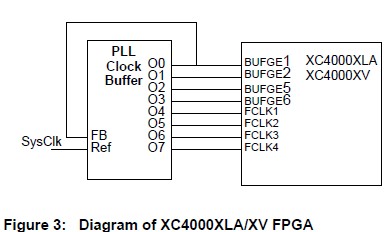

Diagrams

|

XC4000 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000A |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000E |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000H |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000X |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

XC4000XL |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)